CREE C2M0080120D

| (5 intermediate revisions by one user not shown) | |||

| Line 1: | Line 1: | ||

== Download == | == Download == | ||

| − | {{#dlmodel: C2M0080120D | http://www.igbtmodel.org/ | + | {{#dlmodel: C2M0080120D | http://www.igbtmodel.org/index.php?title=File:C2M0080120D.zip }} |

== Identification tool == | == Identification tool == | ||

| Line 8: | Line 8: | ||

=== Static === | === Static === | ||

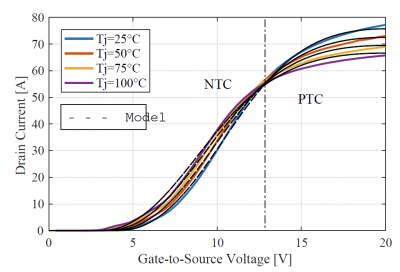

| − | Fig. 1 reports the comparison between the | + | Fig. 1 reports the comparison between the experimental DC Transfer curves and the simulated static output characteristics at different junction temperature values. It can be observed as the current capabilty of the MOSFET increases for higher temperatures when the gate voltage is low (NTC: negative temperature coefficient), while it decreases when Vgs is high (PTC: positive temperature coefficient). |

{| style="margin: 0 auto;" | {| style="margin: 0 auto;" | ||

|- | |- | ||

| − | | [[File:C2M0080120D ID VGS.png|link=|thumb|400px|Fig. 1. DC Transfer Characteristics.]] | + | | [[File:C2M0080120D ID VGS.png|link=|thumb|400px|Fig. 1. DC Transfer Characteristics validation.]] |

|- | |- | ||

|} | |} | ||

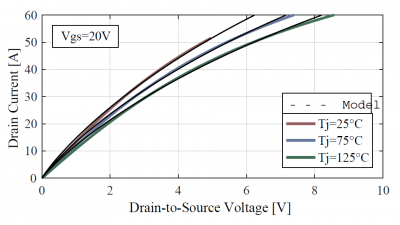

| + | Fig. 2 reports the comparison between the experimental DC Output curves and the simulated static characteristics at different junction temperature values. | ||

{| style="margin: 0 auto;" | {| style="margin: 0 auto;" | ||

|- | |- | ||

| − | | [[File:C2M0080120D ID VDS.png|link=|thumb|400px|Fig. 2. DC | + | | [[File:C2M0080120D ID VDS.png|link=|thumb|400px|Fig. 2. DC Transfer Characteristics validation.]] |

| + | |- | ||

| + | |} | ||

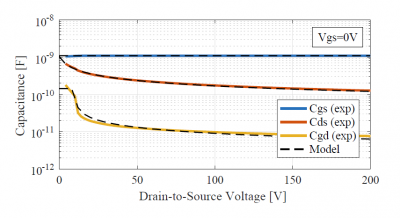

| + | Fig. 4 reports the comparison between the experimental capacitance measurements for a drain bias sweep (Vgs=0) and the simulated curves. | ||

| + | {| style="margin: 0 auto;" | ||

| + | |- | ||

| + | | [[File:C2M0080120D cap.png|link=|thumb|400px|Fig. 3. Capacitance measurements validation.]] | ||

| + | |- | ||

| + | |} | ||

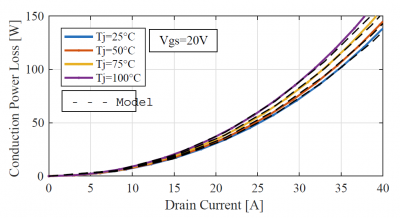

| + | Fig. 4 reports the comparison between the measured conduction power losses and the simulated ones for increasing drain current and different junction temperatures. | ||

| + | {| style="margin: 0 auto;" | ||

| + | |- | ||

| + | | [[File:C2M0080120D condloss.png|link=|thumb|400px|Fig. 4. Conduction power losses validation.]] | ||

|- | |- | ||

|} | |} | ||

=== Dynamic === | === Dynamic === | ||

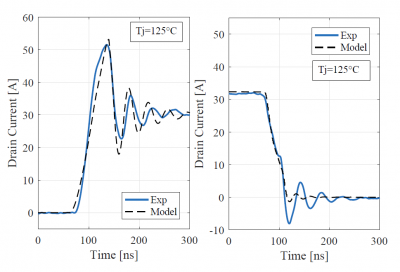

| − | Fig. | + | Fig. 5 and Fig. 6 show the comparison between measured and simulated turn-on and turn-off waveforms for drain current and voltage at the following testing conditions: Id=30 A, Vdc=600V and T=125C. A Double-Pulse test circuit has been used for the measurements, and some parasitic elements have been included in the simulation to emulate the real oscillation of the experimental waveforms. |

{| style="margin: 0 auto;" | {| style="margin: 0 auto;" | ||

|- | |- | ||

| − | | [[File: | + | | [[File:C2M0080120D current validation.png |link=|thumb|400px|Fig. 5. Validation of the drain current switching waveform.]] |

|- | |- | ||

|} | |} | ||

| − | + | {| style="margin: 0 auto;" | |

| + | |- | ||

| + | | [[File:C2M0080120D voltage validation.png |link=|thumb|400px|Fig. 6. Validation of the drain voltage switching waveform.]] | ||

| + | |- | ||

| + | |} | ||

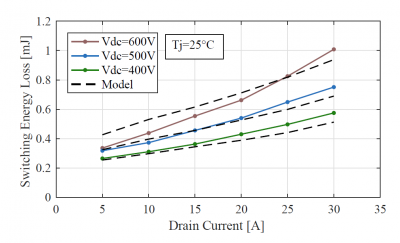

| + | Fig. 7 reports the comparison between the measured switching energy losses and the ones estimated by the model at room temperature, for increasing drain current and for different DC bus voltage values. | ||

| + | {| style="margin: 0 auto;" | ||

| + | |- | ||

| + | | [[File:C2M0080120D sw loss validation.png |link=|thumb|400px|Fig. 7. Validation of the switching energy losses.]] | ||

| + | |- | ||

|} | |} | ||

Latest revision as of 16:17, 22 November 2016

Contents |

[edit] Download

[edit] Identification tool

The parameter extraction has been done by means of a Matlab-PSpice parameter identification tool for SiC MOSFETs called MOSPEX which you can find here. It is a user-friendly Graphic User Interface (GUI) that you can use on your own.

[edit] Tests performed

[edit] Static

Fig. 1 reports the comparison between the experimental DC Transfer curves and the simulated static output characteristics at different junction temperature values. It can be observed as the current capabilty of the MOSFET increases for higher temperatures when the gate voltage is low (NTC: negative temperature coefficient), while it decreases when Vgs is high (PTC: positive temperature coefficient).

Fig. 2 reports the comparison between the experimental DC Output curves and the simulated static characteristics at different junction temperature values.

Fig. 4 reports the comparison between the experimental capacitance measurements for a drain bias sweep (Vgs=0) and the simulated curves.

Fig. 4 reports the comparison between the measured conduction power losses and the simulated ones for increasing drain current and different junction temperatures.

[edit] Dynamic

Fig. 5 and Fig. 6 show the comparison between measured and simulated turn-on and turn-off waveforms for drain current and voltage at the following testing conditions: Id=30 A, Vdc=600V and T=125C. A Double-Pulse test circuit has been used for the measurements, and some parasitic elements have been included in the simulation to emulate the real oscillation of the experimental waveforms.

Fig. 7 reports the comparison between the measured switching energy losses and the ones estimated by the model at room temperature, for increasing drain current and for different DC bus voltage values.